- #CPUSIM INSTRUCTION MEMORY SERIAL#

- #CPUSIM INSTRUCTION MEMORY FULL#

- #CPUSIM INSTRUCTION MEMORY SOFTWARE#

- #CPUSIM INSTRUCTION MEMORY CODE#

If the instruction cannot proceed for any reason (invalid instruction, incorrect mode etc.) go to 7.

#CPUSIM INSTRUCTION MEMORY SERIAL#

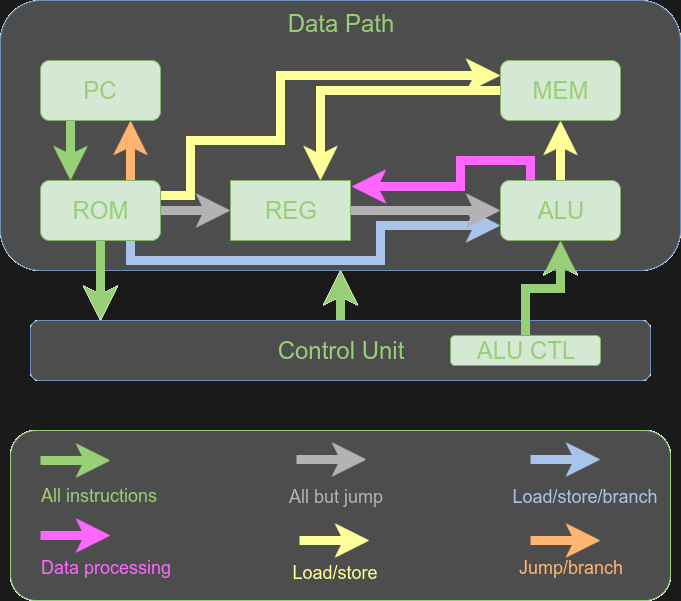

It is sometimes integrated with simulated peripheral circuits such as timers, interrupts, serial ports, general I/O ports, etc. GDB is one debugger which has a compiled-in ISS.

#CPUSIM INSTRUCTION MEMORY SOFTWARE#

This only works for same-on-same instruction-set simulation, such as running x86 simulators on x86 hosts, or ARM simulators on ARM hosts.Īn ISS is often provided with (or is itself) a debugger in order for a software engineer/ programmer to debug the program prior to obtaining target hardware.

#CPUSIM INSTRUCTION MEMORY CODE#

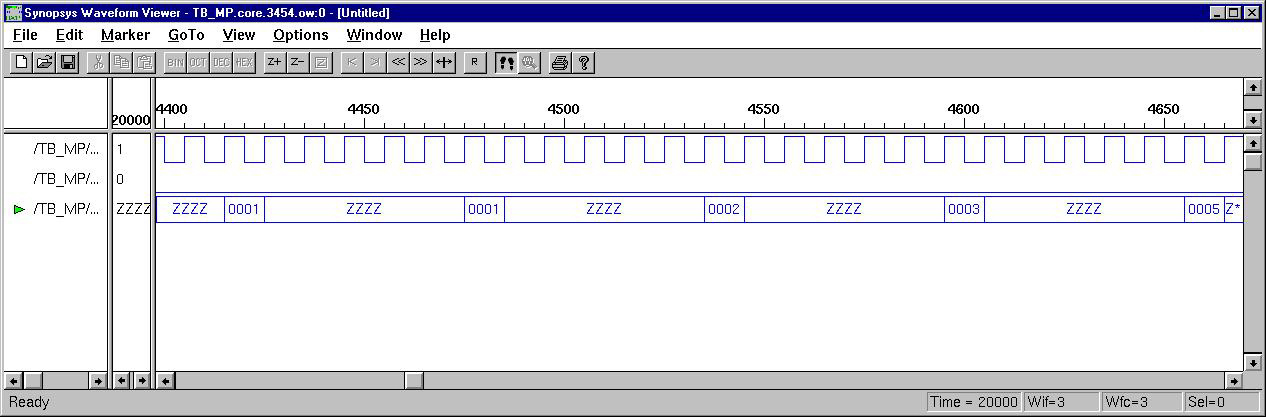

Just-in-time compilation (JIT), where the code to be executed is first translated into the instruction set of the host computer.Interpretation, where each instruction is executed directly by the ISS.Instruction-set simulators can be implemented using three main techniques: To improve the speed performance-compared to a slower cycle-accurate simulator-of simulations involving a processor core where the processor itself is not one of the elements being verified in hardware description language design using Verilog where simulation with tools like ISS can be run faster by means of " PLI" (not to be confused with PL/1, which is a programming language).with memory protection (which protects against accidental or deliberate buffer overflow). To monitor and execute the machine code instructions (but treated as an input stream) on the same hardware for test and debugging purposes, e.g.To simulate the machine code of another hardware device or entire computer for upward compatibility.įor example, the IBM 1401 was simulated on the later IBM/360 through use of microcode emulation.

#CPUSIM INSTRUCTION MEMORY FULL#

A full system simulator or virtual platform for the future hardware typically includes one or more instruction set simulators. This is often known as "shift-left" or "pre-silicon support" in the hardware development field.

JSTOR ( June 2009) ( Learn how and when to remove this template message)Īn instruction set simulator (ISS) is a simulation model, usually coded in a high-level programming language, which mimics the behavior of a mainframe or microprocessor by "reading" instructions and maintaining internal variables which represent the processor's registers.Unsourced material may be challenged and removed.įind sources: "Instruction set simulator" – news Please help improve this article by adding citations to reliable sources. This article needs additional citations for verification.

0 kommentar(er)

0 kommentar(er)